واليوم نأخذ طرق ربط المعالج 8086 مع

الذاكرة:

في الفترة التي ظهر فيها المعالج 8086 كان يتوافر في الأسواق ذواكر طول كلمتها 8 بت، صممت هذه الذواكر للتوافق مع المعالجات الأقدم التي عرض خطوط معطياتها أيضًا 8 بت، مثل المعالج 8085 .

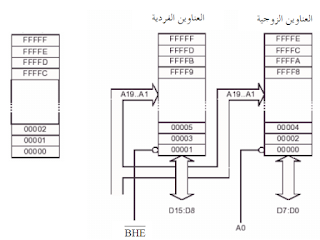

إن عرض مسرى المعطيات في المعالج 8086 هو 16 بت، وبالتالي يمكن للمعالج أن يتبادل خلال دورة آلة واحدة، مع التجهيزات المحيطية، معطيات بطول بايت أو بطول 2 بايت. ولكي يستفيد المعالج 8086 من الذواكر بطول 8 بت، جرى تقسيم فضاء ذاكرة المعالج إلى كتلتين banks , حجم كل منهما 512 كيلوبايت. تضم إحدى الكتل المواقع ذات العناوين الفردية بينما تضم الكتلة الثانية المواقع ذات العناوين الزوجية. تو صل خطوط معطيات الكتلة الفردية إلى خطوط المعطيات D0-D7 وخطوط معطيات الكتلة الزوجية إلى خطوط المعطيات D8-D15 من المعالج، كما هو مبين في الصورة التالية :

يجري انتخاب أي موقع ذاكرة في إحدى الكتلتين باستخدام خطوط العنونة A1-D19 ,بينما يجري انتخاب الكتلة ذات العناوين الفردية باستخدام A0 , والزوجية باستخدام BHE'.

عندما يتبادل المعالج بايتًا مع موقع زوجي من الذاكرة فإنه يجعل A0 =0 و BHE =1 , لانتخاب الكتلة الزوجية. وعندما يريد المعالج تبادل بايت مع موقع فردي فإنه يجعل A0 =1 و BHE =0 , لانتخاب الكتلة الفردية. بينما يجعل المعالج A0=0 و BHE'=0 عندما يتبادل كلمة من 2 بايت مع

موقع ذاكرة يبدأ بعنوان زوجي. ولكن عندما يتبادل المعالج كلمة من 2 بايت مع موقع ذاكرة يبدأ بعنوان فردي فتجري عملية التبادل على مرحلتين، يجري في الأولى تبادل البايت الأولى من الكلمة مع الموقع ذي العنوان الفردي، في حين يجري تبادل البايت الثانية من الكلمة مع الموقع ذي العنوان الزوجي.

إن جميع عمليات العنونة السابقة شفافة بالنسبة للمبرمج، حيث يرى المبرمج فضاء ذاكرة المعالج 8086 كتتابع من البايتات عددها 1 ميغابايت، تبدأ بالعنوان 00000h وتنتهي بالعنوان FFFFFh.

يحتوي كل موقع ذاكرة معطيات بطول 8 بت، كما يمكن أن يشكل أي بايتين متتالين في الذاكرة كلمة بطول 16 بت.

اختبار ذاتي:

بفرض أن BX=F000h , ما هي حالة خطي العنونة A0 و BHE' خلال دورة القراءة عند تنفيذ التعليمة MOV DH, [BX] ؟

الجواب:

بما أن هذه التعليمة تقرأ بايتًا من عنوان زوجي من الذاكرة، فإنه في هذه الحالة يكون A0 =0 و BHE =1 .

اختبار ذاتي:

بفرض أن BX=A200h , ما هي حالة خطي العنونة A0 و BHE' خلال دورة القراءة عند تنفيذ التعليمة MOV [BX], CX ؟

الجواب:

تكتب هذه التعليمة 2 بايت (محتوى CX ) في الذاكرة، وبما أنه يجري كتابة كلمة في موقع زوجي من الذاكرة فتجري عملية الكتابة خلال دورة كتابة واحدة، يكون فيها A0 =0 و BHE =0 .

عند تواجه أو ربط الذواكر مع معالج صغري نوصل إشارة كتابة المعالج WR' مع مدخل إشارة

الكتابة للذواكر. ولكن نظرًا لكون المعالج 8086 يمكن أن يكتب في الكتلة الزوجية أو الكتلة

الفردية على نحو منفصل، فيجب اشتقاق إشارة كتابة في الكتلة الزوجية LWR' وأخرى للكتابة في الكتلة الفردية HWR' تبين الصورة

التالية إحدى الطرق الممكنة لاشتقاق الإشارتين LWR' و HWR' من خطوط العنونة A0 و BHE' وإشارة الكتابة WR' .

مثال: يبين الشكل التالي نظام ذاكرة يحوي 128 كيلوبايت ذاكرة EPROM و 128 كيلوبايت ذاكرة SRAM يمكن ربطه مع معالج 8086 يتضمن هذا النظام:

- أربع ذواكر للقراءة فقط EPROM من طراز 27128 ، يبلغ حجم كل منها 16 كيلوبايت. تكون هذه الذواكر بمجموعها ذاكرة EPROM بحجم 32 كيلو * 16 بت، وتحتل المواقع من F0000h-FFFFFh .

- أربع ذواكر للقراءة والكتابة SRAM من طراز 62256 ، يبلغ حجم كل منها 32 كيلوبايت. تكون هذه الذواكر بمجموعها ذاكرة SRAM بحجم 64 كيلو * 16 بت، وتحتل المواقع من 00000h-1FFFFh .

نستخدم، في هذا النظام، جزءًا من الرقاقة 74LS139 لانتخاب الذواكر EPROM والجزء الآخر من الرقاقة نفسها لانتخاب الذواكر SRAM لاحظ أن كل مخرج من مخارج الرقاقة 74LS139 ينتخب ذاكرة عرض كلمتها 16 بت.

يجري في النظام وصل الإشارة LWR' إلى المدخل WE للذواكر ذات العناوين الزوجية بينما يجري وصل HWR' إلى المدخل WE للذواكر ذات العناوين الفردية. لا حظ أيضًا أننا لم نشتق إشارة قراءة للكتلة الزوجية وأخرى للكتلة الفردية وإنما وصلنا إشارة القراءة RD' من المعالج مباشرة إلى المدخل OE' للذواكر EPROM و RAM في هذه الحالة يقرأ المعالج دومًا 16 بت من الذاكرة ويتجاهل المعالج البايت الذي لا يحتاجه عندما يقرأ المعالج بايتًا واحدًا فقط من الذاكرة.

أخيرًا، يجب أن يكون انتخاب الذواكر EPEOM او SRAM مشروطًا بكون M/IO' =1 , لكون الذواكر تقع في فضاء ذاكرة المعالج. وبالتالي، يجري تمرير الإشارة M/IO' مع خطي العنونة A18 و A19 إلى بوابة NAND يكون خرج هذه البوابة فعالا) يساوي 0 منطقي ( عندما تكون جميع مداخلها تساوي 1 منطقي.

يمكنك ايضا مشاهدة :

الدرس الثاني معالجات 4CISC و معالجات RISC - computer interface

الدرس الثالث المعالجات التواردية pipelining

الدرس الخامس المتحكمات الصغرية Microcontroller

الدرس السابع البنية الداخلية للمعالج 8088/ 8086

الدرس الثامن السجلات الداخلية للمعالج 8088/ 8086

الدرس التاسع تنظيم ذاكرة المعالج 8086

الدرس العاشر انماط العنونة addressing modes

الدرس الحادي غشر البرمجة بلغة التجميع assembly language

الدرس الثاني عشر موجِّهات او ايعازات لغة التجميع Assembler Directives

الدرس الثالث عشر تعليمات المعالج 8088/ 8086 - لغة التجميع

الدرس الرابع عشر تعليمات القفز المشروط - شرح المعالج 8086

الدرس الخامس عشر تعليمات الإزاحة - شرح المعالج 8086

الدرس السادس عشر تعليمات المكدس - شرح المعالج 8086

الدرس السابع عشر تعليمات الحلقات والدوران اسمبلي- شرح المعالج الدقيق 8086

الدرس الثامن عشر اوامر لغة الاسمبلي - تعليمات IN و OUT و تعليمات السلاسل الحرفية - شرح المعالج الدقيق 8086

الدرس التاسع عشر يتبع شرح المعالج 8086 – التعليمات CMPS , SCAS, LODS , STOS , REPNZ , REPNE ،REPZ،REPE ،REP

الدرس العشرين architecture memory معمارية الذاكرة

الذرس الواحد والعشرين أنواع الذواكر - لغة التجميع وشرح المعالج 8086

الى اللقاء في التدوينة القادمة

لا تنسى دعمنا بالمشاركة

دمت بالف خير عزيزنا الزائر

الله يعطيكم الف عافيه

ردحذفواياك ياغالي كم اسعدنا ذلك ... البسك الله ثوب العافية

حذفشكراااااااااا

ردحذفعفواااااااا سررت بمرورك

حذف