اخذنا في التدوينة السابقة المسجلات في وحدة المعالجة المركزية - و بنية (architecture )الذاكرة في المعالج

واليوم نأخذ بنية الذاكرة او معمارية الذاكرة architecture memory

تتكون الذاكرة من عدة سجلات، ويحدد طول هذه السجلات طول كلمة الذاكرة.

تبين الصورة التالية

أربع سجلات موضوعة على التوالي طول كل منها 8 بت.

نحتاج عند الكتابة أو القراءة من أحد هذه السجلات إلى اختيار أو تأهيل ذلك السجل.

يمكننا تأهيل أحد السجلات باستخدام

مفكك ترميز

decoder 2 إلى

4 2-

to 4)) .

نحتاج

في هذه الحالة إلى مدخلين إضافيين A0 و A1 يؤخذان من خطوط عنونة

address

lines المعالج.

تشكل قيمة A0 و A1 أربع ثنائيات مختلفة: 00 , 10 ،01 و 11 تُحدد أو تعنون كل تشكيلة أحد السجلات: register 0 إلى .register 3جرى

الاستعاضة، في الشكل، عن EN بالخطين A0 و .A1

عند زيادة عدد السجلات في الشكل السابق إلى 8 فإننا نصبح بحاجة إلى 3

خطوط عنونة لعنونة أي سجل أو موقع في الذاكرة. وعلى نحو عام يلزمنا log2 L خط عنونة في حالة ذاكرة تضم L سجلاً.

اختبار ذاتي: ما

هو عدد خطوط العنونة اللازمة لعنونة ذاكرة بحجم 1024 بايت؟

الحل: .log21024 =10

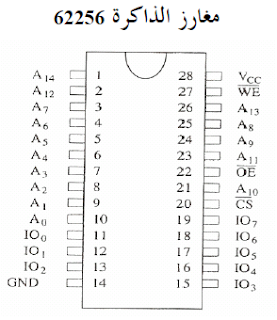

تبين

الصورة التالية مثالا نمطيًا عن ذاكرة للقراءة والكتابة )تسمى أيضًا الذاكرة الحية( وعلى

المغارز التي تتضمنها. تضم مغارز الذاكرة 62256 ، التي يبلغ حجمها 8 32 K

×بت، خطوط

العنونة والمعطيات وإشارات التحكم التالية:

-

خطوط الذاكرة: تضم

الذاكرة 15 62256 خط عنونة .(A0-A14) 62256 ويجري وصل هذه الخطوط إلى خطوط عنونة المعالج، عند وضع الذاكرة في نظام مبني حول معالج.

خطوط المعطيات: تضم الذاكرة 62256

ثماني خطوط معطيات (D0-D7

) , وبالتالي يمكننا تخزين بايت واحد في أي موقع من الذاكرة. ُتوصل خطوط المعطيات إلى خطوط معطيات المعالج

يمكنك متابعة الدروس السابقة من الروابط التالية

الدرس الثاني معالجات 4CISC و معالجات RISC - computer interface

الدرس الثالث المعالجات التواردية pipelining

الدرس الخامس المتحكمات الصغرية Microcontroller

الدرس السابع البنية الداخلية للمعالج 8088/ 8086

الدرس الثامن السجلات الداخلية للمعالج 8088/ 8086

الدرس التاسع تنظيم ذاكرة المعالج 8086

الدرس العاشر انماط العنونة addressing modes

الدرس الحادي غشر البرمجة بلغة التجميع assembly language

الدرس الثاني عشر موجِّهات او ايعازات لغة التجميع Assembler Directives

الدرس الثالث عشر تعليمات المعالج 8088/ 8086 - لغة التجميع

الدرس الرابع عشر تعليمات القفز المشروط - شرح المعالج 8086

الدرس الخامس عشر تعليمات الإزاحة - شرح المعالج 8086

الدرس الخامس عشر تعليمات الإزاحة - شرح المعالج 8086

الدرس السادس عشر تعليمات المكدس - شرح المعالج 8086

الدرس السابع عشر تعليمات الحلقات والدوران اسمبلي- شرح المعالج الدقيق 8086

الدرس الثامن عشر اوامر لغة الاسمبلي - تعليمات IN و OUT و تعليمات السلاسل الحرفية - شرح المعالج الدقيق 8086

الدرس التاسع عشر يتبع شرح المعالج 8086 – التعليمات CMPS , SCAS, LODS , STOS , REPNZ , REPNE ،REPZ،REPE ،REP

الى اللقاء في التدوينة القادمة

لا تنسى دعمنا بالمشاركة

دمت بالف خير عزيزنا الزائر

إرسال تعليق

لا تبخل علينا باقتراحك او قم بمشاركة الموضوع ليستفيد الاخرين ايضاً شكرا لزيارتك عزيزي الزائر