كانت التدوينة السابقة والتي صنفناها تحت بند الدرس الاول وتحمل العنوان ( بحث في تاريخ عائلات المعالجات CPU – computer interface ) .

واليوم ايها الاحبة نواصل معكم مسيرنا في computer interface ونتحدث عن معالجات risc and cisc كما سنذكر الفرق بين معالجات RISC ومعالجات CISC (difference between risc and cisc processor )...

إذن ماهو المعالج cisc ياترى ؟؟ (what is cisc processor ??? ) وماهي بنيتة؟ ( what architecture of risc processor ???)

هذا ما سنعرفة اليوم وهو الدرس الثاني من computer interface

اولاً المعالجات ذات مجموعة التعليمات الموسّعة 4CISC - computer interface

لم تكن تقنية المترجمات compiler متوفرة البتة خلال الفترة الأولى من إنتاج المعالجات، مما حَصر كتابة البرنامج إما برماز الآلة أو بلغة التجميع. ولتسهيل عملية البرمجة وتحسين أداء المعالج، أضاف مصممو المعالجات، في كل مرة، تعليمات معقدة تسمح بتنفيذ وظائف ُتماثل الوظائف التي تقدمها اليوم لغات البرمجة العالية المستوى. ساعد المضي في هذا التوجه، في تلك الفترة، سهولة تصميم الكيان الجامد hardware وصعوبة تصميم المترجمات، مما دفع أكثر نحو ازدياد تعقيد الكيان الجامد. كانت هذه الفكرة وراء تصميم معالجات ذات "مجموعة التعليمات الموسعة" او CISC مثل عائلة المعالجات x86 من Intel التي تضم مجموعة تعليماتها أكثر من 300 تعليمة. تتميز معالجات CISC بكثرة عدد أنماط العنونة والسجلات وكذلك بالطول المتغير لكود التعليمات.

أدى ازدياد تعقيد الكيان الجامد وبنيان المعالج إلى صعوبة فهمه وبرمجته وإلى ارتفاع كلفة إنتاجه.

نذكر من المعالجات CISC الشائعة: العائلة x86 والعائلة Motorola 68000 و AMD .

ثانياً المعالجات ذات مجموعة التعليمات الموجزة :RISC(Reduce Instruction Set Computers)

شهد منتصف الثمانينات بداية ظهور البنيان RISC استوحيت هذه الفلسفة بعد الدراسة التي أظهرت أن العديد من الميزات الموجودة في وحدات المعالجة المركزية، والمصممة لتسهيل برمجته، يجري تجاهلها من قبل المبرمج عند كتابته للبرنامج. أضف على ذلك، الزمن الكبير الذي يأخذه المعالج لتنفيذ التعليمات المعقدة، واتساع الفجوة بين سرعة المعالجة والذاكرة الرئيسة. كل ذلك أدى إلى تطوير العديد من التقنيات تجعل عمل المعالج أكثر انسيابية، مع الإقلال بالوقت نفسه من عدد مرات النفوذ إلى الذاكرة.

تعتمد فكرة RISC على أن الطريقة الأفضل لتحسين أداء المعالج تكمن في تبسيط عمله ما أمكن. على سبيل المثال، اختزلت عدد تعليمات المعالج IBM PowerPC وهو من نوع RISC ، إلى حوالي 100 تعليمة أو أقل، وأعيد تبسيط أنماط العنونة إلى أربعة أو أقل، كما جُعل طول التعليمة ثابتًا من أجل جعل مجموعة التعليمات معيارية.

نذكر من المعالجات RISC الشائعة ،PIC ،PA-RISC ،MIPS ،AVR ،ARM ،Alpha ،Power Architecture و SPARC

أدى التحول نحو البنيان RISC إلى استخدام عدد أقل من الترانزستور في إنتاج المعالجات، مما يجعل كلفة إنتاج الرقاقات RISC أقل بكثير من كلفة إنتاج نظيرها CISC.

كذلك فإن اختزال عدد التعليمات يعني أن المعالج يمكنه أن ينفذ التعليمات بسرعة أعلى، ولكن نظرًا لقلة عدد التعليمات فمن الضروري استخدام التعليمات المتاحة على نحو فعال.

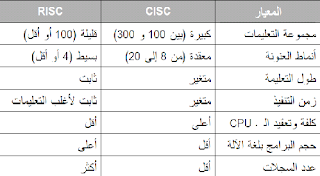

يبين الجدول التالي مقارنة بين البنيانين RISC و CISC

difference between risc and cisc processor

بالنظر إلى المعالجات الحديثة، نجد أن المنافسة بين RISC و CISC ليس له اليوم أهمية كبيرة، وهذا بسبب تقارب هذان البنيانان كل منهما باتجاه الأخر، حيث أن وحدات المعالجة CPUs من كل بنيان تتبنى أفكار البنيان الآخر. فالمعالجات CISC تستخدم العديد من التقنيات الموجودة في RISC كما أن عدد التعليمات الموجزة لمعالجات RISC قريبة من تلك الموجودة في بعض معالجات CISC .

واليوم ايها الاحبة نواصل معكم مسيرنا في computer interface ونتحدث عن معالجات risc and cisc كما سنذكر الفرق بين معالجات RISC ومعالجات CISC (difference between risc and cisc processor )...

إذن ماهو المعالج cisc ياترى ؟؟ (what is cisc processor ??? ) وماهي بنيتة؟ ( what architecture of risc processor ???)

هذا ما سنعرفة اليوم وهو الدرس الثاني من computer interface

لم تكن تقنية المترجمات compiler متوفرة البتة خلال الفترة الأولى من إنتاج المعالجات، مما حَصر كتابة البرنامج إما برماز الآلة أو بلغة التجميع. ولتسهيل عملية البرمجة وتحسين أداء المعالج، أضاف مصممو المعالجات، في كل مرة، تعليمات معقدة تسمح بتنفيذ وظائف ُتماثل الوظائف التي تقدمها اليوم لغات البرمجة العالية المستوى. ساعد المضي في هذا التوجه، في تلك الفترة، سهولة تصميم الكيان الجامد hardware وصعوبة تصميم المترجمات، مما دفع أكثر نحو ازدياد تعقيد الكيان الجامد. كانت هذه الفكرة وراء تصميم معالجات ذات "مجموعة التعليمات الموسعة" او CISC مثل عائلة المعالجات x86 من Intel التي تضم مجموعة تعليماتها أكثر من 300 تعليمة. تتميز معالجات CISC بكثرة عدد أنماط العنونة والسجلات وكذلك بالطول المتغير لكود التعليمات.

أدى ازدياد تعقيد الكيان الجامد وبنيان المعالج إلى صعوبة فهمه وبرمجته وإلى ارتفاع كلفة إنتاجه.

نذكر من المعالجات CISC الشائعة: العائلة x86 والعائلة Motorola 68000 و AMD .

ثانياً المعالجات ذات مجموعة التعليمات الموجزة :RISC(Reduce Instruction Set Computers)

شهد منتصف الثمانينات بداية ظهور البنيان RISC استوحيت هذه الفلسفة بعد الدراسة التي أظهرت أن العديد من الميزات الموجودة في وحدات المعالجة المركزية، والمصممة لتسهيل برمجته، يجري تجاهلها من قبل المبرمج عند كتابته للبرنامج. أضف على ذلك، الزمن الكبير الذي يأخذه المعالج لتنفيذ التعليمات المعقدة، واتساع الفجوة بين سرعة المعالجة والذاكرة الرئيسة. كل ذلك أدى إلى تطوير العديد من التقنيات تجعل عمل المعالج أكثر انسيابية، مع الإقلال بالوقت نفسه من عدد مرات النفوذ إلى الذاكرة.

تعتمد فكرة RISC على أن الطريقة الأفضل لتحسين أداء المعالج تكمن في تبسيط عمله ما أمكن. على سبيل المثال، اختزلت عدد تعليمات المعالج IBM PowerPC وهو من نوع RISC ، إلى حوالي 100 تعليمة أو أقل، وأعيد تبسيط أنماط العنونة إلى أربعة أو أقل، كما جُعل طول التعليمة ثابتًا من أجل جعل مجموعة التعليمات معيارية.

نذكر من المعالجات RISC الشائعة ،PIC ،PA-RISC ،MIPS ،AVR ،ARM ،Alpha ،Power Architecture و SPARC

أدى التحول نحو البنيان RISC إلى استخدام عدد أقل من الترانزستور في إنتاج المعالجات، مما يجعل كلفة إنتاج الرقاقات RISC أقل بكثير من كلفة إنتاج نظيرها CISC.

كذلك فإن اختزال عدد التعليمات يعني أن المعالج يمكنه أن ينفذ التعليمات بسرعة أعلى، ولكن نظرًا لقلة عدد التعليمات فمن الضروري استخدام التعليمات المتاحة على نحو فعال.

يبين الجدول التالي مقارنة بين البنيانين RISC و CISC

difference between risc and cisc processor

بالنظر إلى المعالجات الحديثة، نجد أن المنافسة بين RISC و CISC ليس له اليوم أهمية كبيرة، وهذا بسبب تقارب هذان البنيانان كل منهما باتجاه الأخر، حيث أن وحدات المعالجة CPUs من كل بنيان تتبنى أفكار البنيان الآخر. فالمعالجات CISC تستخدم العديد من التقنيات الموجودة في RISC كما أن عدد التعليمات الموجزة لمعالجات RISC قريبة من تلك الموجودة في بعض معالجات CISC .

نلتقي في التدوينة القادمة بعنوان المعالجات التواردية pipelining

لا تنسى الاشتراك في المدونة ليصلك كل جديدنا

الف شكر اولا لهذا المجهود المميز هل من محتوى عربي يفصل الية عمل كل نوع

ردحذفلا شكر على واجب لقد اسعدتني زيارتك maan younis ,,, بالنسبة لاستفسارك ,, ربما تجد محتوى عربي اذا بحثت ,,,,

ردحذفعاشت الايادي وبرافو عليك معلومات دقيقه جدا

ردحذف