تعتبر هذه التدوينات والتي نعتبرها سلسلة من الدروس في الدوائر

الموائمة computer

interface

والمعالجات الدقيقة CPU ، تفيد

وبشكل كبير طلاب هندسة الحاسوب ، كذلك علوم الحاسوب ، حيث وانها من ضمن مقررهم

الدوائر الموائمة ، computer interface

قد تحتاج الإطلاع على الدروس السابقة اليك روابطها :

الدرس الاول : بحث في تاريخ عائلات المعالجات CPU – computer interface

سنتعرف في درس اليوم على المعالجات السلمية الفائقة Superscalar كما سنتعرف على بنيان ڤون نومان وبنيان هارفرد..

إن

تطبيق مبدأ التوارد Pipelining يزيد من سرعة تنفيذ المعالج للتعليمات؛ فبينما تُحمِّل وحدة المعالجة المركزية تعليمة جديدة فإنها تنفذ حسابات التعليمة التي سبقتها وتخزن نتيجة التعليمة التي سبقت سابقتها. صحيح

أن هذه المعالجة تعتبر تفرعية إلا أنها لا تعتبر معالجة سلمية فائقة superscalar processing لكونها تُنهي على الأكثر تعليمة واحدة خلال كل دورة آلة.

لزيادة

معدل تنفيذ التعليمات عمدت بعض الشركات إلى تصنيع معالجات عالية الأداء تحتوي على عدة وحدات حسابية ومنطقية ALU تعمل معًا على التوازي. تستطيع هذه المعالجات جلب عدة تعليمات بآن واحد وفك ترميز عدد من التعليمات السابقة وتنفيذ عدد من التعليمات التي سبقت سابقتها.

تُبرمج

هذه الوحدات بتعليمات مشفرة على عدد كبير من البتات )مثلا

96 بت)، تسمى بالتعليمات ذات الكلمات العريضة جدًا .Very Large Instruction Word (VLIW) توصف هذه المعالجات بأنها معالجات سلمية فائقة

Superscalar .

تزداد

سرعة المعالجة مع ازدياد عدد الوحدات في المعالج. فبينما تحتوي المعالجات السلمية الفائقة الأولى على وحدتي حساب منطقية ALU ووحدة حساب بالفاصلة العائمة، نجد أن المعالجات الحديثة، مثل PowerPC 970 ،

تحتوي

على أربع وحدات حساب منطقية ووحدتي حساب بالفاصلة العائمة .

يشار

عادة إلى المعالج 6600

CDC

من Seymour Cray

على

أنه أول تصميم لمعالج سُلمي فائق، بينما المعالجات i 960 من Intel

عام

1988 ) وسلسلة) 29000 AMD

عام (1990 ) هي أول معالج تجاري من نوع Superscalar ومنذ العام 1988 فإن أغلب المعالجات للاستخدام العام هي من نوع Superscalar ، منها معالجات بنتيوم التي تحتوي على وحدتي حساب للأعداد الصحيحة، يمكنهما العمل معًا إذا توافرت الشروط الملائمة لذلك.

المعالجات

ذات

بنيان

هارڤرد Harvard

اعتمد

تصميم المعالجات في البدء على استخدام بنيان ذاكرة نفسه لتخزين التعليمات والمعطيات وكذلك المساري نفسها من أجل النفاذ إلى ذاكرة البرنامج وذاكرة المعطيات، تعرف هذه التقانة ببنيان ڤون نومان von Neumann .

في

هذا البنيان يمكن للمعالج في آنٍ واحد إما أن يقرأ تعليمة أو يقرأ/يكتب

معطيات في الذاكرة، كما ينفذ التعليمات تعليمة تلو الأخرى على نحو تتابعي إلا إذا جرى تغيير هذا التتابع من قبل تعليمات البرنامج، مثل تعليمات القفز.

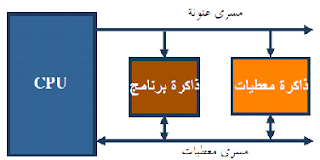

الصورة تبين بنية فون نومان

ولتحسين

أداء المعالجات، اعتمدت بعض الشركات المصنعة بنيانًا ذو مسريين مستقلين:

المسرى

الأول: يتصل بذاكرة البرنامج، ويجري من خلاله قراءة التعليمات من الذاكرة إلى المعالج.

المسرى

الثاني: يتصل بذاكرة المعطيات، ويسمح بتبادل المعطيات بين الذاكرة الحية RAM والمعالج كما في الصورة

يسمح

الفصل بين مسرى ذاكرة البرنامج ومسرى ذاكرة المعطيات بتسريع عمل المعالج، حيث يستطيع المعالج جلب التعليمة القادمة بينما ينهي تخزين ناتج التعليمة الحالية، بالطبع هناك ثمن لهذا التسريع وهو زيادة عدد مغارز الرقاقة IC مما يجعل توصيل المعالج داخل النظام معقدًا.

كما

تسمح عملية الفصل أيضًا باستخدام بنية مختلفة لكل من ذاكرة البرنامج وذاكرة المعطيات؛ فنجد مثلا أن حجم كلمة التعليمة في المعالجات الحديثة أكبر من حجم كلمة المعطيات، كما أن ذاكرة البرنامج غالبًا ما تكون من نوع الميتة (للقراءة فقط) بينما

نستخدم ذاكرة حية (للقراءة والكتابة) لتخزين المعطيات المؤقتة.

يُستخدم

بنيان هارفرد كثيرًا في معالجات الإشارة الرقمية، والمتحكمات الصغرية.

نكتفي بهذا القدر ونلتقي في التدوين القادم او الدرس الخامس بعنوان المتحكمات

الصغرية Microcontroller.

عزيزنا الزائر إن كانت هذه اول زيارة لك لمدونتنا لا تنسى الاشتراك

فيها عبر بريدك الالكتروني ليصلك كل جديد او قم بالإعجاب بصفحتنا على الفيس بوك في

يسار الصفحة ....

رائع شكرا لكم

ردحذفالعفو شكراُ لزيارتك المشرفة

حذفشكراً

ردحذف